您的 ASIC 设计是否需要尽可能低的泄漏和尽可能小的面积?您想采用 FinFET 技术,但又担心昂贵的晶圆成本?台积电 22nm 工艺提供了一个令人信服的选择。我们看到许多曾经使用 28 纳米、40 纳米及以上工艺的 Arm 合作伙伴,现在正在向 22 纳米工艺迁移,以实现更低的泄漏和更小的面积,从而保持甚至提高所需的性能。

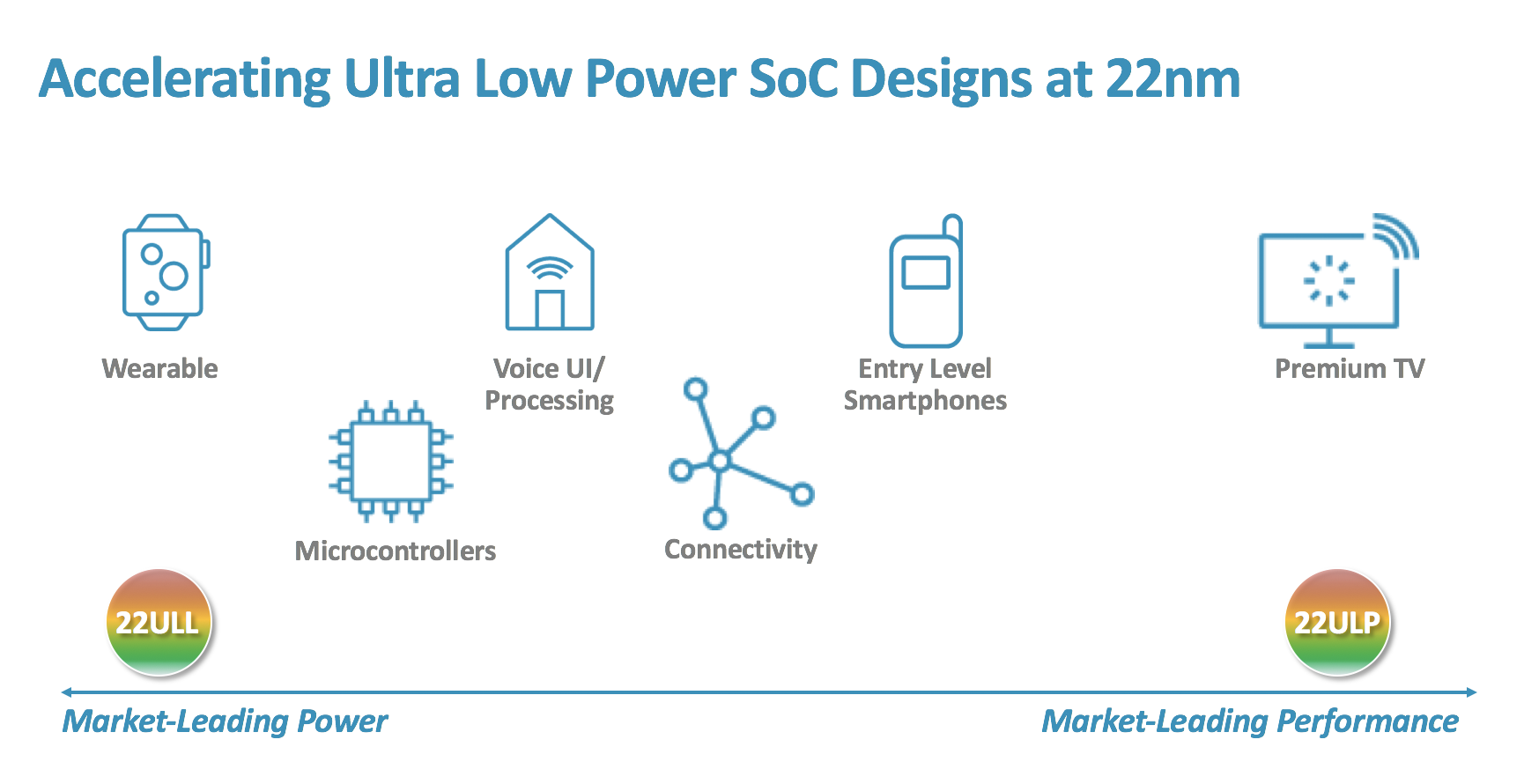

台积电 22nm 技术是基于台积电业界领先的 28nm 工艺开发的,该工艺在性能、功耗和面积扩展方面是许多不同细分市场的首选代工解决方案。然而,一些集成电路设计人员正在寻找一种经济的方法,以满足数字电视、机顶盒、智能手机和消费类产品等应用对性能提升和更低电源电压的要求。与 28 纳米工艺相比,台积电 22 纳米工艺能显著减少面积、提高速度并降低功耗,是以低成本提高性能和降低功耗的最佳途径。

Arm 的合作伙伴之一Ambiq Micro 是一家领先的无线连接和智能传感技术许可商,一直在与 Arm 合作从 40 纳米升级到 22 纳米。Ambiq 使用 Arm IP,包括Cortex-M、Crypto、CoreSight SoC-400、ETM、TSMC 22ULL 存储器和 TGO 库,实现了具有嵌入式安全性的亚阈值泄漏。Arm 解决方案的部分优势包括

- 采用 UHVT/HVT 器件的 ULL-ULL 内存编译器可提供尽可能低的泄漏,同时满足高达 500MHz 的性能要求。

- 6V 外围电压支持有助于降低物联网应用的功耗。

- 厚栅极氧化物 (TGO) 进一步减少了漏电,因为在薄栅极氧化物和厚栅极氧化物之间设计了特殊的电平转换器,可在 0.8v 至 3.3v 之间转换。

根据 Ambiq 的反馈,Arm Artisan 存储器编译器与竞争对手的 IP 相比,面积缩小了 5%,泄漏减少了 4%,同时达到了相同的性能标准。

台积电支持用于台积电 22 纳米 ULP 和 ULL 工艺技术的 Artisan 存储器编译器。这些编译器针对低漏电和低功耗要求进行了优化。有关 Ambiq 最新超低功耗和高性能设计以及 Arm 解决方案如何提供帮助的更多详情,请访问 Ambiq 和 Arm 在台积电虚拟技术研讨会和 OIP 生态系统论坛上的在线网站。