未来几年,全球将新增数十亿台智能设备,因此能效对于实现全天候连接的物联网设备至关重要。过去,大多数物联网设计都是在 40nm 或更大的几何尺寸上实现的,但如今我们看到许多 Arm 合作伙伴正在从这些成熟技术向 22nm 迁移。

为什么 22 纳米工艺是物联网的理想选择?显然,从 40 纳米甚至更高的工艺节点转向 22 纳米工艺具有性能优势,但要注意的是,原始性能并不是衡量物联网设计的正确尺度。相反,最好的衡量标准是特定计算任务的能耗。而这正是 22 纳米工艺的优势所在。

后起之秀:22 纳米超低功耗和超低泄漏

台积电的 22 纳米技术是在其业界领先的 28 纳米工艺基础上开发出来的,该工艺是针对需要性能、功耗和面积扩展的各种应用的首选代工解决方案。台积电的 28 纳米制程技术具有高性能和低功耗的优势,并能与 28 纳米设计生态系统无缝集成,从而加快产品上市时间。它使产品能够提供更高的性能,降低能耗,并在数年内保持环保。

台积电 22 纳米超低功耗(22ULP)和 22 纳米超低漏电(22ULL)技术源自 28 纳米技术。与 28 纳米高性能紧凑型 (28HPC) 技术相比,22ULP 技术在降低功耗和提高速度方面有显著改进。这些特性通常是某些移动和消费应用(如笔记本电脑和数字电视 (DTV))所需要的。新型 ULL 器件和 ULL SRAM(静态随机存取存储器)可显著降低功耗,这对于物联网和可穿戴设备的设计至关重要。

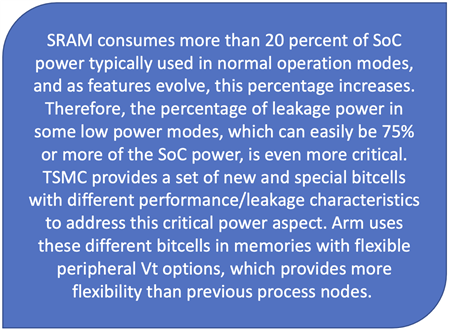

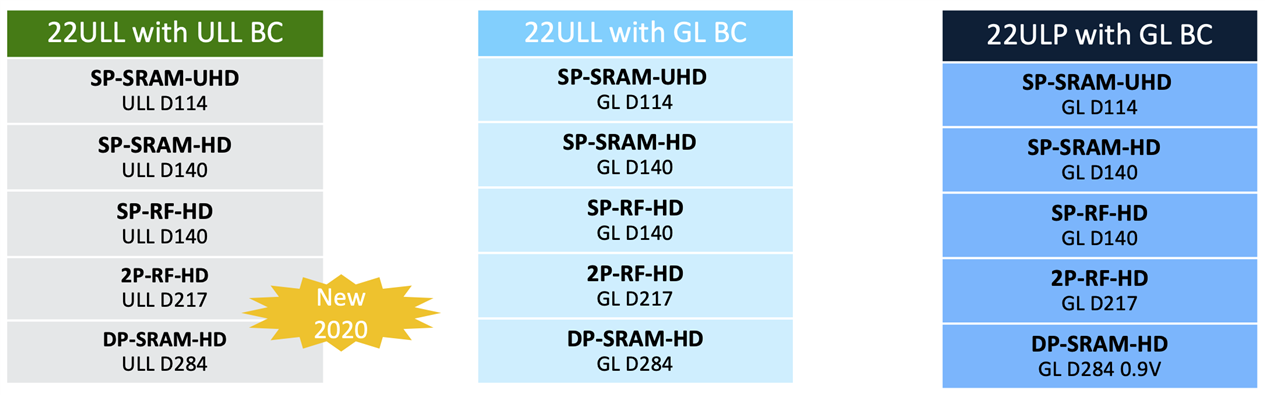

根据产品的不同,SoC 设计人员可以选择面向性能的 22ULP 工艺或面向物联网的低功耗 22ULL 工艺。基于台积电提供的 12 种不同位元,Arm 为 22ULL 和 22ULP 开发了 15 种由台积电赞助的 SRAM/RF 编译器,并计划开发更多。用于 22ULL 的编译器针对低漏电和低功耗要求进行了优化,提供了多种省电功能。设计人员在使用 22ULL 进行设计时,可在面向性能的 GL 和低功耗 ULL 位元系列中进行选择。22ULP 编译器基于 GL 位元。

采用 TSMC 22ULL 和 Arm 物联网解决方案设计的 Ambiq

对于给定的计算任务,TSMC 22ULL 的能耗要求远低于 50%,是物联网应用的完美技术。作为无线连接和智能传感技术的领先授权厂商,Ambiq 在其最新产品组合Apollo4 SoC 系列中采用了台积电 22ULL 技术和 Arm 物联网解决方案。Apollo4 SoC 系列为实现智能边缘物联网设备的超低功耗 SoC 设立了新标准,并为所有电池供电的边缘设备提供了提高系统能力与降低功耗的完美结合。

Apollo4 SoC 系列采用 TSMC 22ULL 工艺、带浮点运算单元 (FPU) 的 32 位Arm®Cortex®-M4内核和Artisan 物理 IP,通过 MRAM 实现了无与伦比的低功耗睡眠模式。利用 AmbiqturboSPOT®– Ambiq 的超低功耗动态性能扩展技术,它的时钟频率最高可达 192MHz。它建立在 Ambiq 的SPOT®平台上,使 CPU 和内存以更高的频率(HP)运行。Apollo4 SoC 系列具有加速 2/2.5D 图形、MIPI DSI、高达 640×480 和 32 位色彩,以及支持始终在线语音命令应用的超低功耗模拟麦克风,专门为电池供电的边缘设备(包括智能手表、健身手环、远程控制、预测性健康和维护工具以及智能家电)设计,既可用作应用处理器,也可用作协处理器。

灵活性再上新台阶

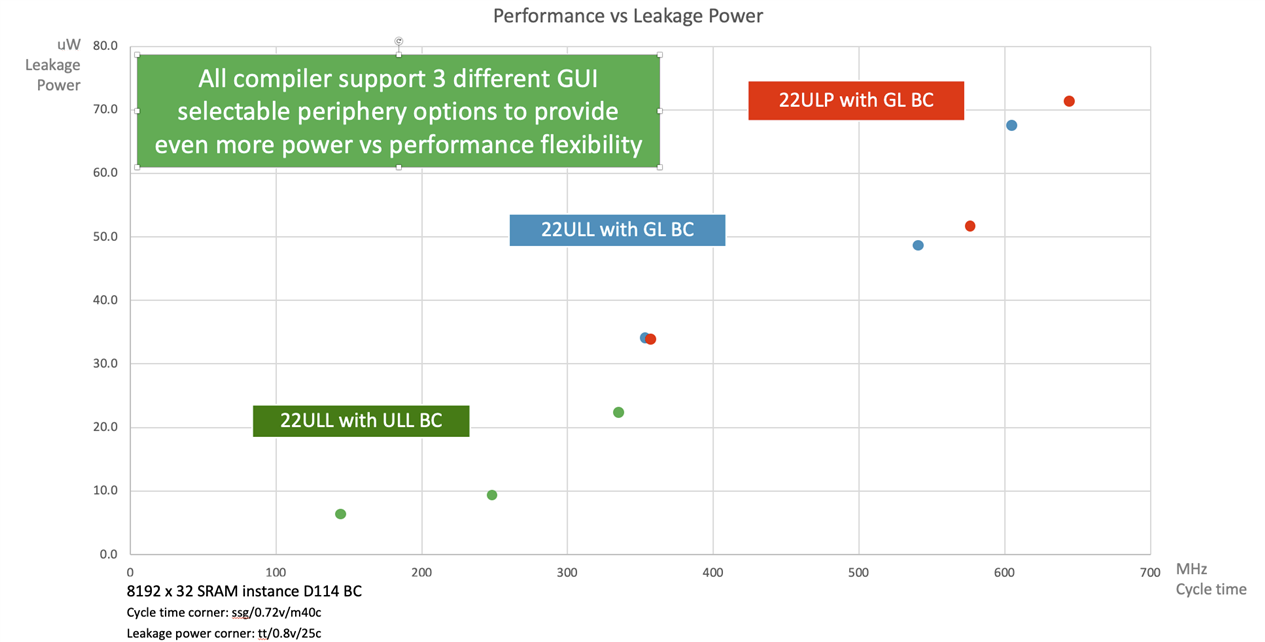

TSMC 22ULL 和 Arm 物联网产品将灵活性提升到了一个新的水平,使制造商能够设计各种应用。但灵活性并不止于此。利用各种逻辑器件的多种外围选择,SoC 设计师现在可以使用台积电 22nm 工艺进行 GHz 范围内的性能导向型设计或 <100MHz 的超低功耗设计。下图显示了使用高密度位元组的编译器的功耗性能范围,分别为使用 GL 位元组的 22ULP、使用 GL 位元组的 22ULL 和使用 ULL 位元组的 22ULL。这三种编译器还各有三种外围选项。

台积电 22nm 工艺的灵活性与 Arm Artisan 物理 IP 相结合,实现了广泛的物联网应用,例如采用 Cortex-M4 的低功耗 Ambiq Apollo4 SoC。采用Cortex-M55和Ethos-U55 等较新 Arm 内核的设计可以在要求苛刻的边缘 AI 应用中实现更大的优势。

目前有 100 多家客户在台积电 22 纳米工艺上积极使用 Arm 物理 IP。Arm 的目标是帮助合作伙伴取得成功。如需物理 IP 和 POP IP 设计,请立即联系Arm。